| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: HT1622 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

Document Outline

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

- ˛ˇ

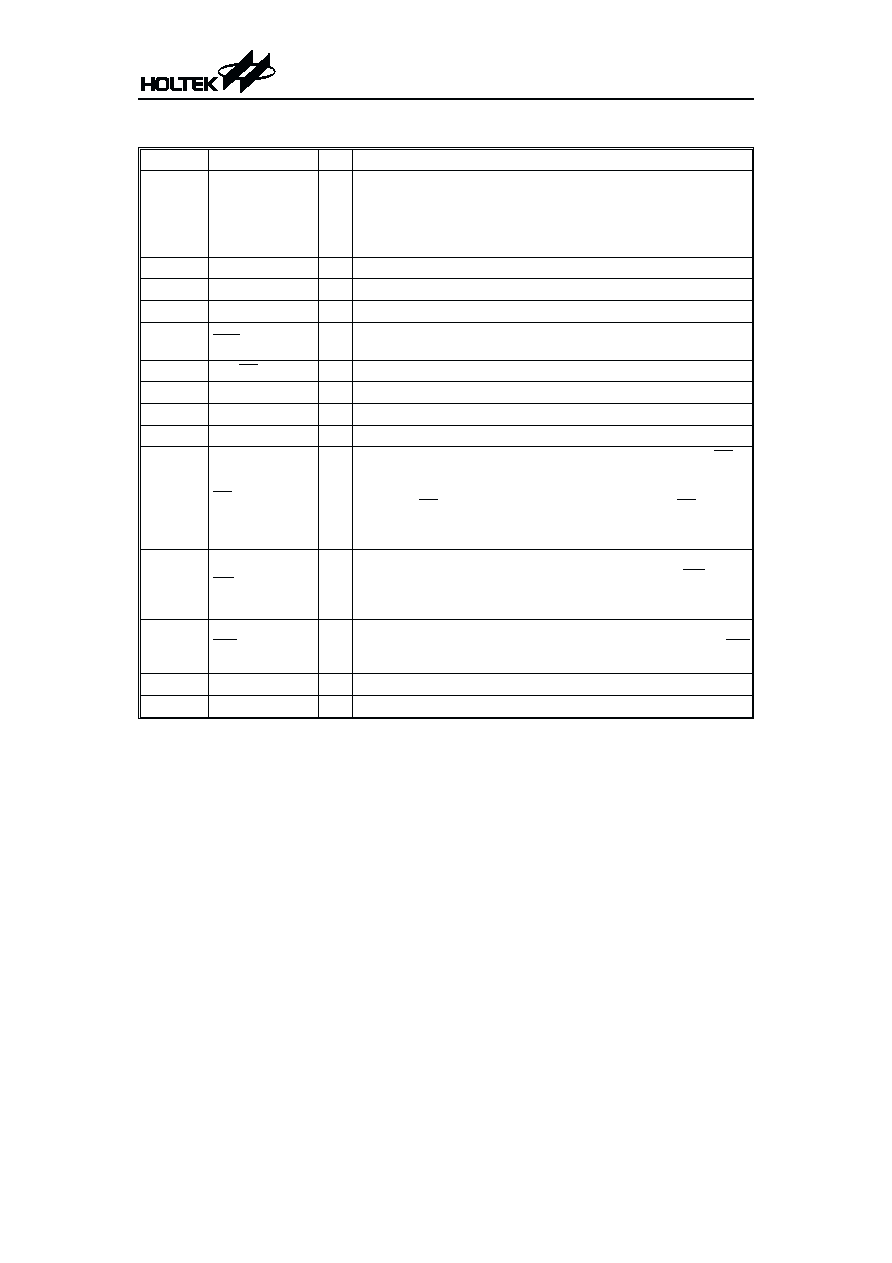

HT1626

RAM Mapping 48¥16 LCD Controller for I/O mC

Selection Table

HT162X

HT1620 HT1621 HT1622 HT16220 HT1623 HT1625 HT1626 HT1627 HT16270

COM

4

4

8

8

8

8

16

16

16

SEG

32

32

32

32

48

64

48

64

64

Built-in Osc.

÷

÷

÷

÷

÷

÷

Crystal Osc.

÷

÷

÷

÷

÷

÷

÷

1

April 21, 2000

Features

∑

Operating voltage: 2.7V~5.2V

∑

Built-in RC oscillator

∑

External 32.768kHz crystal or 32kHz

frequency source input

∑

1/5 bias, 1/16 duty, frame frequency is 64Hz

∑

Max.48¥16patterns,16commons,48segments

∑

Built-in internal resistor type bias generator

∑

3-wire serial interface

∑

8 kinds of time base/WDT selection

∑

Time base or WDT overflow output

∑

Built-in LCD display RAM

∑

R/W address auto increment

∑

Two selection buzzer frequencies

(2kHz/4kHz)

∑

Power down command reduces power

consumption

∑

Software configuration feature

∑

Data mode and Command mode instructions

∑

Three data accessing modes

∑

VLCD pin to adjust LCD operating voltage

∑

Cascade application

General Description

HT1626 is a peripheral device specially de-

signed for I/O type mC used to expand the dis-

play capability. The max. display segment of

the device are 768 patterns (48¥16). It also sup-

ports serial interface, buzzer sound, Watchdog

Timer or time base timer functions. The

HT1626 is a memory mapping and

multi-function LCD controller. The software

configuration feature of the HT1626 make it

suitable for multiple LCD applications includ-

ing LCD modules and display subsystems. Only

three lines are required for the interface be-

tween the host controller and the HT1626. The

HT162X series have many kinds of products

that match various applications.

Block Diagram

Pin Assignment

HT1626

2

April 21, 2000

V L C D

W R

SE

G

2

SE

G

0

SE

G

1

SE

G

3

SE

G

6

H T 1 6 2 6

1 0 0 Q F P

3 1 3 2 3 3 3 4 3 5 3 6 3 7 3 8 3 9 4 0 4 1 4 2 4 3 4 4 4 5 4 6 4 7 4 8 4 9 5 0

8 1

8 2

8 3

8 4

8 5

8 6

8 7

8 8

8 9

9 0

9 1

9 2

9 3

9 4

9 5

9 6

9 7

9 8

9 9

1 0 0

8 0

7 9

7 8

7 7

7 6

7 5

7 4

7 3

7 2

7 1

7 0

6 9

6 8

6 7

6 6

6 5

6 4

6 3

6 2

6 1

6 0

5 9

5 8

5 7

5 6

5 5

5 4

5 3

5 2

5 1

D A T A

O S C O

V D D

I R Q

SE

G

4

SE

G

5

SE

G

7

SE

G

8

SE

G

1

0

SE

G

1

1

SE

G

1

2

SE

G

1

3

SE

G

1

4

SE

G

1

5

SE

G

1

6

S E G 1 7

S E G 1 8

SE

G

3

4

SE

G

4

2

SE

G

4

1

SE

G

4

0

SE

G

3

9

SE

G

3

8

SE

G

3

7

SE

G

3

6

SE

G

3

5

SE

G

4

3

SE

G

3

3

SE

G

3

2

SE

G

3

1

SE

G

3

0

S E G 1 9

SE

G

4

7

SE

G

4

6

SE

G

4

5

SE

G

4

4

O S C I

N C

N C

CO

M

1

3

CO

M

1

4

CO

M

1

5

1

2

3

4

5

6

7

8

9

1 0

1 1

1 2

1 3

1 4

1 5

1 6

1 7

1 8

1 9

2 0

2 1

2 2

2 3

2 4

2 5

2 6

2 7

2 8

2 9

3 0

RD CS

V S S

T 1

B Z

B Z

T 2

T 3

T 4

C O M 0

C O M 1

C O M 2

C O M 3

C O M 4

N C

C O M 5

C O M 6

C O M 7

C O M 8

C O M 9

C O M 1 0

C O M 1 1

C O M 1 2

SE

G

9

N C

N C

N C

N C

N C

N C

N C

S E G 2 4

S E G 2 5

S E G 2 7

S E G 2 6

S E G 2 9

S E G 2 8

N C

N C

N C

N C

N C

N C

N C

N C

N C

N C

S E G 2 0

S E G 2 1

S E G 2 2

S E G 2 3

W a t c h d o g T i m e r

a n d

T i m e B a s e G e n e r a t o r

D i s p l a y R A M

L C D D r i v e r /

B i a s C i r c u i t

C o n t r o l

a n d

T i m i n g

C i r c u i t

D A T A

W R

O S C I

C S

R D

C O M 0

C O M 1 5

S E G 0

S E G 4 7

T o n e F r e q u e n c y

G e n e r a t o r

B Z

B Z

I R Q

V S S

V D D

V L C D

O S C O

Pad Assignment

Chip size: 242 ¥ 196 (mil)

2

* The IC substrate should be connected to VDD in the PCB layout artwork.

HT1626

3

April 21, 2000

DA

T

A

VS

S

O S C O

O S C I

V D D

V L C D

B Z

T 1

T 2

T 3

C O M 0

C O M 1

C O M 2

C O M 3

C O M 4

CO

M

5

CO

M

6

CO

M

7

SE

G

0

SE

G

1

SE

G

2

SE

G

3

SE

G

4

SE

G

5

SE

G

6

SE

G

7

SE

G

8

SE

G

9

SE

G

1

0

SE

G

1

1

SE

G

1

2

SE

G

1

3

SE

G

1

4

SE

G

1

5

SE

G

1

6

SE

G

1

7

SE

G

1

8

SE

G

1

9

SE

G

2

0

SE

G

2

1

SE

G

2

2

SE

G

2

3

SE

G

2

5

SE

G

2

4

SE

G

2

6

SE

G

2

7

SE

G

2

8

SE

G

2

9

SE

G

3

0

SE

G

3

1

SE

G

3

2

SE

G

3

3

SE

G

3

4

SE

G

3

5

SE

G

3

6

SE

G

3

7

SE

G

3

8

SE

G

3

9

SE

G

4

0

SE

G

4

1

SE

G

4

2

SE

G

4

3

SE

G

4

4

SE

G

4

5

SE

G

4

6

SE

G

4

7

RD

WR

I R Q

B Z

CS

1

4 1

2

4 2

3

4 3

4

4 4

5

4 5

6

4 6

7

4 7

8

4 8

9

4 9

1 0

5 0

1 1

5 1

1 2

5 2

1 3

5 3

1 4

5 4

1 5

5 5

1 6

5 6

1 7

5 7

1 8

5 8

1 9

5 9

2 0

6 0

2 1

6 1

2 2

6 2

2 3

6 3

2 4

6 4

2 5

6 5

2 6

6 6

2 7

6 7

2 8

6 8

2 9

6 9

3 0

7 0

3 1

7 1

3 2

7 2

3 3

7 3

3 4

7 4

3 5

7 5

3 6

7 6

3 7

7 7

3 8

7 8

3 9

7 9

4 0

8 0

T 4

CO

M

8

CO

M

9

CO

M

1

0

CO

M

1

1

CO

M

1

2

CO

M

1

3

CO

M

1

4

CO

M

1

5

( 0 , 0 )

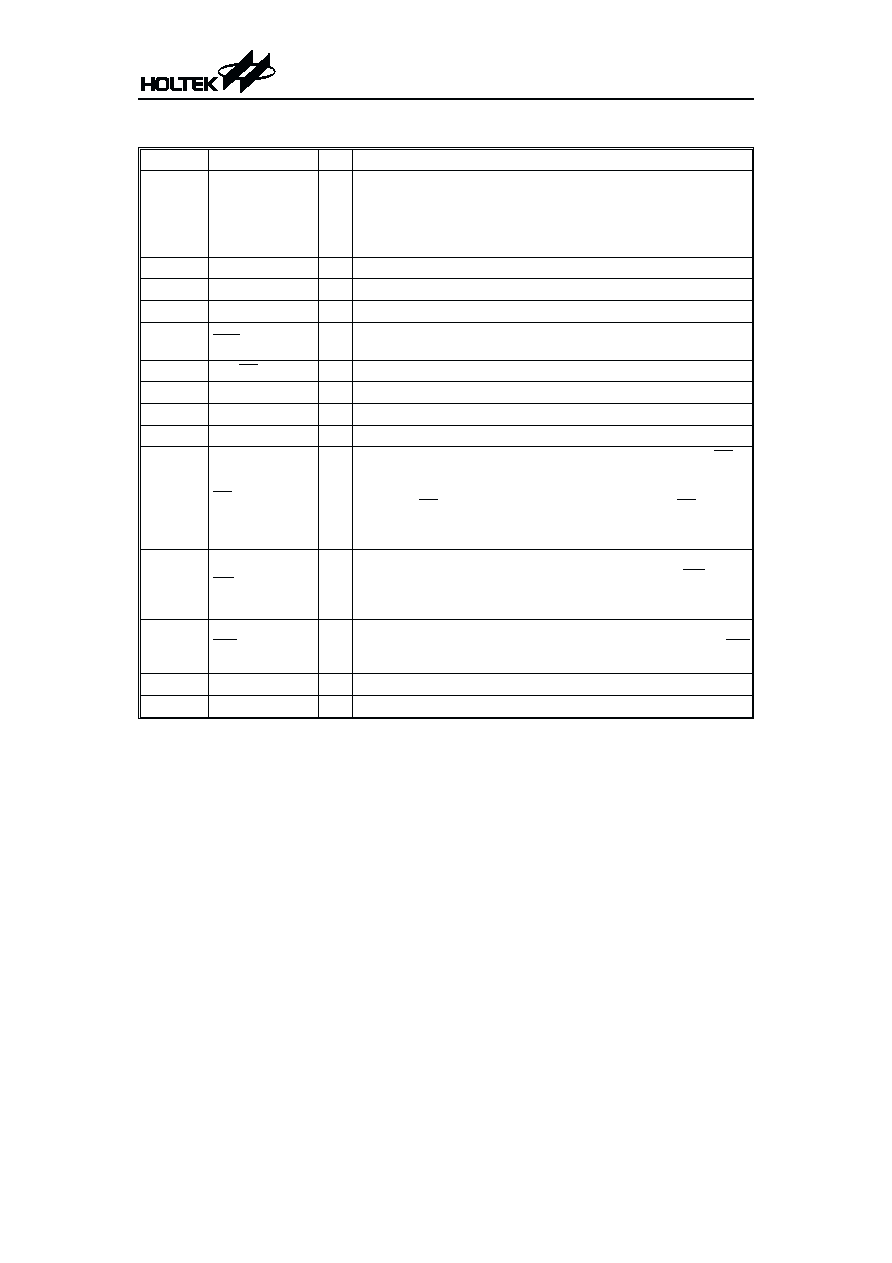

Pad Coordinates

Unit: mil

Pad No.

X

Y

Pad No.

X

Y

1

-115.68

77.99

41

47.47

-92.74

2

-115.68

71.36

42

54.10

-92.74

3

-113.69

54.83

43

60.73

-92.74

4

-114.92

46.62

44

67.36

-92.74

5

-115.68

37.10

45

73.99

-92.74

6

-115.68

23.80

46

80.62

-92.74

7

-115.68

4.21

47

87.25

-92.74

8

-114.92

-6.29

48

93.88

-92.74

9

-114.92

-18.27

49

100.51

-92.74

10

-114.92

-24.91

50

107.14

-92.74

11

-114.92

-36.89

51

113.77

-92.74

12

-114.92

-43.52

52

114.88

92.74

13

-114.92

-55.51

53

108.25

92.74

14

-114.92

-62.13

54

101.62

92.74

15

-114.92

-74.12

55

94.99

92.74

16

-114.92

-80.75

56

88.36

92.74

17

-114.92

-92.74

57

81.73

92.74

18

-105.02

-92.74

58

75.10

92.74

19

-98.39

-92.74

59

68.47

92.74

20

-91.76

-92.74

60

61.84

92.74

21

-85.13

-92.74

61

55.21

92.74

22

-78.50

-92.74

62

48.58

92.74

23

-71.87

-92.74

63

41.95

92.74

24

-65.24

-92.74

64

35.32

92.74

25

-58.61

-92.74

65

28.69

92.74

26

-51.98

-92.74

66

22.06

92.74

27

-45.35

-92.74

67

15.43

92.74

28

-38.72

-92.74

68

8.80

92.74

29

-32.09

-92.74

69

2.17

92.74

30

-25.46

-92.74

70

-4.46

92.74

31

-18.83

-92.74

71

-11.09

92.74

32

-12.20

-92.74

72

-17.72

92.74

33

-5.57

-92.74

73

-24.35

92.74

34

1.06

-92.74

74

-30.98

92.74

35

7.69

-92.74

75

-37.61

92.74

36

14.32

-92.74

76

-44.24

92.74

37

20.95

-92.74

77

-50.87

92.74

38

27.58

-92.74

78

-57.50

92.74

39

34.21

-92.74

79

-68.04

92.74

40

40.84

-92.74

80

-82.71

91.97

HT1626

4

April 21, 2000

Pad Description

Pad No.

Pad Name

I/O

Description

1

OSCI

I

The OSCI and OSCO pads are connected to a 32.768kHz crystal

in order to generate a system clock. If the system clock comes

from an external clock source, the external clock source should

be connected to the OSCI pad. But if an on-chip RC oscillator is

selected instead, the OSCI and OSCO pads can be left open.

2

OSCO

O

3

VDD

æ Positive power supply

4

VLCD

I

LCD operating voltage input pad.

5

IRQ

O Time base or Watchdog Timer overflow flag, NMOS open drain

output

6, 7

BZ, BZ

O 2kHz or 4kHz tone frequency output pair

8~11

T1~T4

I

Not connected

12~27

COM0~COM15

O LCD common outputs

28~75

SEG0~SEG47

O LCD segment outputs

76

CS

I

Chip selection input with pull-high resistor. When the CS is

logic high, the data and command read from or write to the

HT1626 are disabled. The serial interface circuit is also reset.

But if the CS is at logic low level and is input to the CS pad, the

data and command transmission between the host controller

and the HT1626 are all enabled.

77

RD

I

READ clock input with pull-high resistor. Data in the RAM of

the HT1626 are clocked out on the rising edge of the RD signal.

The clocked out data will appear on the data line. The host con-

troller can use the next falling edge to latch the clocked out data.

78

WR

I

WRITE clock input with pull-high resistor. Data on the DATA

line are latched into the HT1626 on the rising edge of the WR

signal.

79

DATA

I/O Serial data input/output with pull-high resistor

80

VSS

æ Negative power supply, Ground

Absolute Maximum Ratings

Supply Voltage..............................-0.3V to 5.5V

Storage Temperature.................-50∞C to 125∞C

Input Voltage................V

SS

-0.3V to V

DD

+0.3V

Operating Temperature ..............-25∞C to 75∞C

Note: These are stress ratings only. Stresses exceeding the range specified under ≤Absolute Maxi-

mum Ratings≤ may cause substantial damage to the device. Functional operation of this de-

vice at other conditions beyond those listed in the specification is not implied and prolonged

exposure to extreme conditions may affect device reliability.

HT1626

5

April 21, 2000